Дизайнфотоникнэгдсэн хэлхээ

Фотоник интеграл хэлхээ(PIC)-ийг ихэвчлэн математикийн скриптүүдийн тусламжтайгаар зохион бүтээдэг, учир нь интерферометр эсвэл замын уртад мэдрэмтгий бусад хэрэглээнд замын урт чухал ач холбогдолтой байдаг.Зураголон өнцөгт хэлбэрээс бүрдсэн, ихэвчлэн GDSII форматаар дүрслэгдсэн вафли дээр олон давхарга (ихэвчлэн 10-30) хээгээр үйлдвэрлэдэг. Файлыг фото маск үйлдвэрлэгч рүү илгээхээсээ өмнө дизайны зөв эсэхийг шалгахын тулд PIC-ийг дуурайлган хийх боломжтой байх нь зүйтэй. Симуляци нь олон түвшинд хуваагддаг: хамгийн доод түвшин нь гурван хэмжээст цахилгаан соронзон (EM) симуляци бөгөөд симуляцийг долгионы уртаас доогуур түвшинд гүйцэтгэдэг боловч материал дахь атомуудын хоорондын харилцан үйлчлэлийг макроскопийн хэмжээнд зохицуулдаг. Ердийн аргуудад гурван хэмжээст хязгаарлагдмал зөрүүтэй цаг хугацааны домэйн (3D FDTD) болон өөрийн горимын өргөтгөл (EME) орно. Эдгээр аргууд нь хамгийн нарийвчлалтай боловч PIC симуляцийн бүх хугацаанд практик биш юм. Дараагийн түвшин нь хязгаарлагдмал зөрүүтэй цацрагийн тархалт (FD-BPM) гэх мэт 2.5 хэмжээст EM симуляци юм. Эдгээр аргууд нь илүү хурдан боловч зарим нарийвчлалыг алддаг бөгөөд зөвхөн параксиаль тархалтыг зохицуулж чаддаг бөгөөд жишээлбэл резонаторуудыг дуурайлган хийхэд ашиглах боломжгүй. Дараагийн түвшин нь 2D FDTD болон 2D BPM гэх мэт 2D EM симуляци юм. Эдгээр нь мөн илүү хурдан боловч туйлшралын ротаторуудыг симуляци хийж чадахгүй гэх мэт хязгаарлагдмал функцтэй. Цаашдын түвшин бол дамжуулалт болон/эсвэл тархалтын матрицын симуляци юм. Үндсэн бүрэлдэхүүн хэсэг бүрийг оролт болон гаралттай бүрэлдэхүүн хэсэг болгон бууруулж, холбогдсон долгион хөтлөгчийг фазын шилжилт болон сулруулах элемент болгон бууруулна. Эдгээр симуляци нь маш хурдан байдаг. Гаралтын дохиог дамжуулалтын матрицыг оролтын дохиогоор үржүүлснээр олж авдаг. Тархалтын матриц (элементүүдийг S-параметр гэж нэрлэдэг) нь бүрэлдэхүүн хэсгийн нөгөө талын оролт болон гаралтын дохиог олохын тулд нэг талын оролт болон гаралтын дохиог үржүүлдэг. Үндсэндээ тархалтын матриц нь элементийн доторх тусгалыг агуулдаг. Тархалтын матриц нь хэмжээс бүрт дамжуулалтын матрицаас ихэвчлэн хоёр дахин том байдаг. Товчхондоо, 3D EM-ээс дамжуулалт/тархалтын матрицын симуляци хүртэл симуляцийн давхарга бүр хурд болон нарийвчлалын хоорондох буулт хийдэг бөгөөд дизайнерууд дизайны баталгаажуулалтын үйл явцыг оновчтой болгохын тулд өөрсдийн тодорхой хэрэгцээнд тохирсон симуляцийн зөв түвшинг сонгодог.

Гэсэн хэдий ч тодорхой элементүүдийн цахилгаан соронзон симуляцид найдаж, PIC-ийг бүхэлд нь симуляци хийхийн тулд тархалт/шилжүүлэх матриц ашиглах нь урсгалын хавтангийн өмнө бүрэн зөв дизайн хийхийг баталгаажуулдаггүй. Жишээлбэл, буруу тооцоолсон замын урт, өндөр эрэмбийн горимыг үр дүнтэй дарж чадахгүй олон горимт долгион хөтлөгч, эсвэл бие биенээсээ хэт ойрхон байрладаг хоёр долгион хөтлөгч нь гэнэтийн холболтын асуудалд хүргэдэг тул симуляцийн явцад илрэхгүй байх магадлалтай. Тиймээс дэвшилтэт симуляцийн хэрэгслүүд нь дизайны баталгаажуулалтын хүчирхэг чадварыг олгодог ч дизайны нарийвчлал, найдвартай байдлыг хангах, урсгалын хуудасны эрсдэлийг бууруулахын тулд дизайнерын өндөр түвшний сонор сэрэмж, нямбай шалгалт, практик туршлага, техникийн мэдлэгийг шаарддаг.

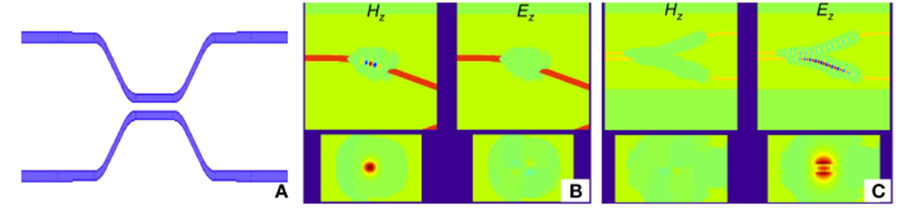

Сийрэг FDTD гэж нэрлэгддэг арга нь дизайныг баталгаажуулахын тулд 3D болон 2D FDTD симуляцийг бүрэн PIC загвар дээр шууд гүйцэтгэх боломжийг олгодог. Цахилгаан соронзон симуляцийн ямар ч хэрэгсэл маш том хэмжээний PIC-ийг дуурайлган хийхэд хэцүү байдаг ч сийрэг FDTD нь нэлээд том орон нутгийн талбайг дуурайж чаддаг. Уламжлалт 3D FDTD-д симуляци нь тодорхой квантлагдсан эзэлхүүн доторх цахилгаан соронзон орны зургаан бүрэлдэхүүн хэсгийг эхлүүлснээр эхэлдэг. Цаг хугацаа өнгөрөх тусам эзэлхүүн дэх шинэ талбайн бүрэлдэхүүн хэсгийг тооцоолдог гэх мэт. Алхам бүр маш их тооцоолол шаарддаг тул удаан хугацаа шаардагддаг. Сийрэг 3D FDTD-д эзэлхүүний цэг бүр дээр алхам бүр дээр тооцоолохын оронд онолын хувьд дур зоргоороо том эзэлхүүнтэй тохирч болох, зөвхөн эдгээр бүрэлдэхүүн хэсгүүдэд тооцоолж болох талбайн бүрэлдэхүүн хэсгүүдийн жагсаалтыг хадгалдаг. Цаг хугацааны алхам бүрт талбайн бүрэлдэхүүн хэсгүүдийн зэргэлдээ цэгүүдийг нэмж, тодорхой чадлын босго хэмжээнээс доогуур талбайн бүрэлдэхүүн хэсгүүдийг хасдаг. Зарим бүтцийн хувьд энэ тооцоолол нь уламжлалт 3D FDTD-ээс хэд дахин хурдан байж болно. Гэсэн хэдий ч сийрэг FDTDS нь тархалтын бүтэцтэй ажиллахад сайн ажилладаггүй, учир нь энэ цагийн талбар хэт их тархдаг тул жагсаалт хэтэрхий урт бөгөөд удирдахад хэцүү болдог. Зураг 1-т туйлшралын цацрагийн хуваагч (PBS)-тэй төстэй 3D FDTD симуляцийн жишээ дэлгэцийн агшинг харуулав.

Зураг 1: 3 хэмжээст сийрэг FDTD-ээс гарсан симуляцийн үр дүн. (A) нь симуляци хийж буй бүтцийн дээд талын харагдац бөгөөд энэ нь чиглэлтэй холбогч юм. (B) Квази-TE өдөөлтийг ашиглан хийсэн симуляцийн дэлгэцийн агшинг харуулж байна. Дээрх хоёр диаграмм нь квази-TE болон квази-TM дохионуудын дээд талын харагдацыг, доорх хоёр диаграмм нь харгалзах хөндлөн огтлолын харагдацыг харуулж байна. (C) Квази-TM өдөөлтийг ашиглан хийсэн симуляцийн дэлгэцийн агшинг харуулж байна.

Нийтэлсэн цаг: 2024 оны 7-р сарын 23